VLSI/Common

[VLSI] Verification vs. Validation

리미와감자

2025. 2. 2. 02:22

[VLSI] Verification vs. Validation

Verification

의미

- Verification은 설계한 RTL Code가 모든 사양(Specification)을 만족하는지 검증하는 과정이다.

- Simulation Level에서 검증하는 단계이다.

- 주어진 사양을 모두 충족했는지 확인하는, 설계자 관점 검증이다.

방법

- Simulation : SystemVerilog, UVM 등을 활용한 테스트벤치(Testbench) 기반 시뮬레이션이다. Class 기반으로 Testbench를 구성하며, 필요에 따라 SVA(SystemVerilog Assertion)을 활용하여 검증한다.

- Formal Verification : 수학적으로 논리적인 오류를 검증한다.

- Coverage Metrics : Code Coverage, Functional Coverage 등을 통해 검증의 충분성을 평가한다.

- FPGA Emulation : FPGA 또는 하드웨어 가속기를 활용하여 빠르게 검증한다.

Validation

의미

- Validation은 설계한 칩이 실제 환경에서 올바르게 동작하는지 확인하는 과정이다.

- 칩이 실제 제품(SoC, ASIC 등)에서 정상적으로 동작하는지를 검증하는 것이 목표이다.

- Verification을 통과한 설계라도 제작 후 물리적인 오류(공정 문제, 전력, 타이밍 이슈 등)가 있을 수 있으므로 Validation이 필요하다.

- Verification에서 Function적으로 문제가 없더라도, Validation에서 다른 환경(다른 모듈과의 연동 등)에서의 Performance를 확인해야 한다.

- 실제 사용자가 사용을 할 때 아무 문제가 없는지 확인하는, 사용자 관점 검증이다.

방법

- FPGA Emulation : FPGA에 RTL을 구현하여 실제 환경에서 동작 여부 확인한다.

- Silicon Bring-Up : 실제 제작된 칩을 보드에 장착하고 테스트한다.

- System-Level Test : 제품 환경에서 테스트하여 호환성 및 성능을 확인한다.

- Power, Performance, Thermal Test : 실제 구동 시의 동작을 측정하여 예상과 일치하는지 확인한다.

Verification vs. Validation

| Verification | Validation | |

|---|---|---|

| 목적 | 설계(RTL)가 사양과 일치하는지 검증 | 실제 칩이 기대한 대로 동작하는지 확인 |

| 대상 | RTL (Register-Transfer Level) | 실리콘(테이프아웃 이후) |

| 방법 | 시뮬레이션, SystemVerilog, UVM, Formal Verification, FPGA Emulation | FPGA Emulation, Silicon Bring-Up, System Test |

| 진행 시점 | 설계 및 개발 중 | 칩 제작 후 (테이프아웃 이후) |

| 발견 가능한 오류 | 논리적 오류, 기능적 오류 | 공정 불량, 타이밍 문제, 전력 문제, 환경적 이슈, 성능 불량 |

| 테스트 환경 | 가상 환경 (Simulation, FPGA) | 실제 하드웨어 환경 |

Is FPGA Emulation a verification or validation?

- FPGA Emulation은 Verification이 될 수도 Validation이 될 수도 있다.

- Spec을 만족하는지 검증하는 용도로 FPGA를 사용하면 Verification, Simulation에서 검증할 수 없는 실제 시스템 환경에서 Performance적인 부분을 확인하는 목적이면 Validation이다.

- 테스트 환경에 따라 구분할 수도 있다. 단순히 Simulation Level이면 모두 Verification이고, HW Level 즉 제품(시스템) 환경이면 모두 Validation이다. 이러한 관점에서는 FPGA Emulation은 Validation이다.

- ASIC 설계가 최종이 아닌 FPGA 설계가 최종이면 FPGA Emulation 자체가 Validation이다.

- 회사마다 또는 팀마다 상황에 따라 용어를 다르게 사용할 수 있음에 주의해야 한다.

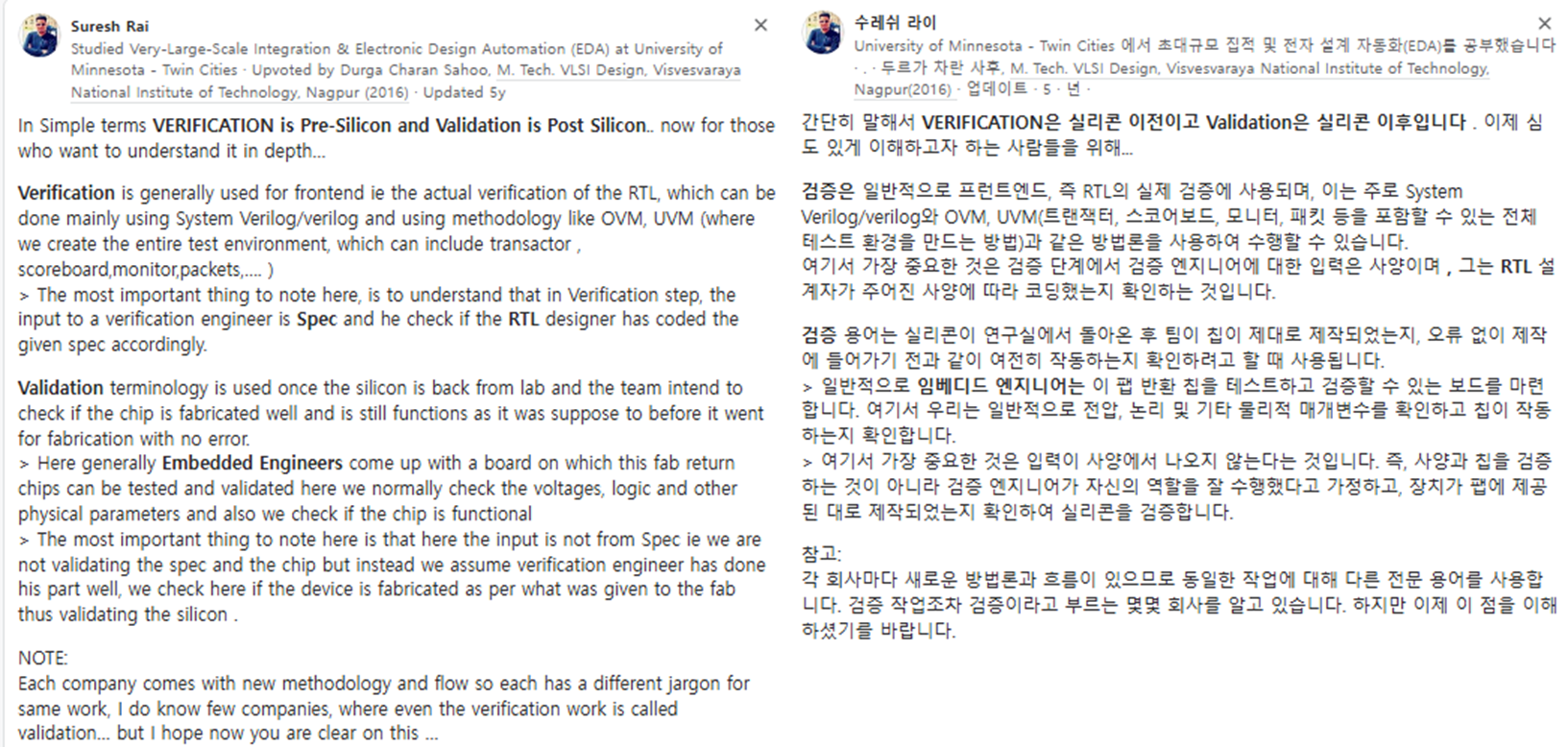

참고 자료

http://verificationexcellence.in/verification-validation-testing-soc/

ASIC and SOC Verification, Validation and Testing in chip design flows

Differences between Verification, Validation and Testing for ASIC and SOC designs in the VLSI and Semiconductor chip design life cycle

verificationexcellence.in